Insbesondere durch den Ausbau erneuerbarer Energien und die Evolution der Elektromobilität wächst das Interesse der Industrie an effizienter und zuverlässiger Leistungselektronik. Die zunehmende Bedeutung der Elektronik führt gleichermaßen zu einer gesteigerten Komplexität der elektronischen Baugruppen mit hohen Strömen und Frequenzen. Zu den Komplexitäten zählen u. a. die Funktionsintegration und die daraus folgende hohe Packungsdichte auf der Leiterplatte, um maximale Funktion in minimaler Form zu schaffen. Besonders schwierig ist die Verarbeitung solcher Leiterplatten mit bedrahteten Bauteilen, den sogenannten THT-Bauteilen (Through Hole Technology). Zur THT-Kontaktierung kommen insbesondere große Bauteile mit hoher Wärmekapazität, wie z. B. Elektrolytkondensatoren, Relais und HF-Stecker zum Einsatz. Die hohe Wärmeempfindlichkeit solcher THT-Bauteile stellt die Fertigung vor anspruchsvolle Herausforderungen hinsichtlich der Wärmezufuhr beim Lötprozess.

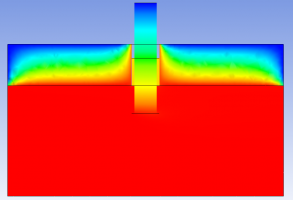

Projektziel des IGF-Vorhabens 19539 N ist die rechnergestützte Beurteilung von Leiterplattendesigns zur Unterstützung im Entwicklungs- und Fertigungsprozess. Durch Versuche und thermische Simulation werden zunächst einzelne Lötstellendesigns etwa wie im Titelbild modelliert um die Einflüsse der Geometrieparameter, wie Kupferlagendicke und Wärmefallengeometrie, zu untersuchen. Zusätzlich werden durch Variation der Prozess- und Materialparameter weitere wichtige Einflussfaktoren abgebildet.

Weitere Informationen finden Sie auf der Projektseite SiWOLAK.

Kontakt:

Dr. Reinhardt Seidel

Department Maschinenbau (MB)

Lehrstuhl für Fertigungsautomatisierung und Produktionssystematik (FAPS, Prof. Franke)

- Telefon: +499115302-99075

- E-Mail: reinhardt.seidel@faps.fau.de